Die meisten FPGA Hersteller bieten vorgefertigte Controller für DDR3 RAM ICs an. Leider ist die Anbindung gerade bei kleinen FPGAs nur 16 oder 32 Bit breit, weshalb Computer DIMMs oder SODIMMs mit einer Breite von 64 Bit (8x8 Bit) nicht vollständig genutzt werden können. Dies liegt unter anderen daran, dass für die hohe Transferrate spezielle Hardwarekomponente innerhalb des FPGAs verwendet werden müssen (u.A. eine DLL für die einzelnen Strobe Leitungen).

Üblicherweise erfordert DDR3 Speicher eine minimale Taktrate von etwa 300 MHz, was eine herkörmliche "manuelle" Implementierung mit den klassischen Logikzellen auf kleinen FPGAs sehr erschwert oder gar unmöglich macht. Allerdings bietet der DDR3 Standard auch einen in der Praxis kaum genutzen "DLL-off" Modus an, in dem es keine untere Grenze für die Taktfrequenz gibt. Alle von mir getesteten Ram Module unterstützen diesen Modus. Der Spezifikation nach scheint er jedoch optional zu sein. Ob es Module auf dem Markt ohne DLL-Off Modus zu kaufen gibt, ist mir nicht bekannt. Nachteil dieses Modus sind höhere Latenzen und eine reduzierte Schreib- und Lesegeschwindigkeit.

Der hier vorgestellte Controller wurde mit Schreib- und Leseraten von etwa 800MiB/s getestet. Eine Erhöhung auf 1200MiB/s halte ich noch für einfach machbar. Die Entwicklung eines vollständigen DDR3 DRAM Speichercontrollers ist signifikant aufwändiger als die für einen statischen RAM (SRAM). Um die Komplexität etwas zu reduzieren, werden die einzelnen Speichertransaktionen hier deshalb strikt nacheinander abgearbeitet, wodurch allerdings zwischen den Transaktionen einige Takte "verloren" gehen, d.h. ungenutzt bleiben. Die angegebene Schreib- und Leserate kann daher nur bei wenigen Transaktionen mit großen zusammenhängenden Speicherblöcken im KiB Bereich erreicht werden und würde sich bei kleinstmöglichen Transaktionen um mehr als den Faktor drei reduzieren. Als Puffer für Hochgeschwindigkeit ADCs/DACs oder Bildsensoren (in meinem Fall) ist dies aber häufig ausreichend, da hier i.d.R. die Daten gestreamed werden.

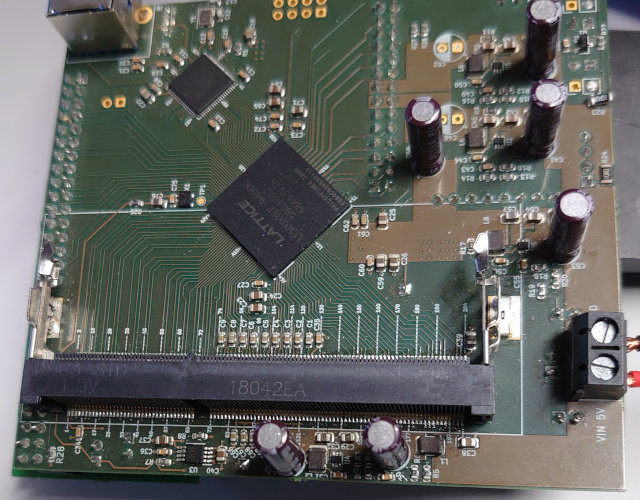

Das folgende Bild zeigt einen Beispielaufbau, in dem ein 4 GiB DDR3 SODIMM 204 Pin Speicherriegel an einen MACHXO3 FPGA der Firma Lattice angebunden wird. Auch größere Module können ohne Änderung der Hardware verwendet werden. Das SODIMM Modul ist fertig gekauft und wird über einen Slot Steckverbinder angeschlossen.

Die gezeigte Platine mit dem FPGA ist dabei eine Eigenentwicklung und besteht aus vier Layern. Auf der Rückseite befindet sich ein Hochgeschwindigkeits Bildsensor (Python 2000 von OnSemi). Das Auslesen der Daten an den Computer geschieht mittels einer FTDI FT601 USB 3.0 Bridge. Weiterhin sind diverse DC/DC Wandler für die verschiedenen Spannungen des Bildsensors, des FPGAs und des DDR3 Speichers (1,5 Volt), ein spezieller Hochstrom Source-Sink-Linear Regler zur Terminierung der Datenleitungen des DDR3 Speichers sowie ein Mikrocontroller, Flash Speicher und USB Hub IC (auf der Rückseite) vorhanden. Die Platine und ein SMD Lötpasten Stencil habe ich bei Aisler fertigen lassen und anschließend selbst bestückt. Die Kosten für den gesamten Aufbau sind noch überschaubar (etwa 400 €).

Ein Vorteil eines eigenen Speicherinterfaces ist, dass die Pin Zuordnung von Ram Speicher an den FPGA fast komplett frei ist und damit das Platinenlayout deutlich vereinfacht wird. Bei einer herkörmlichen Anbindung wären die Strobe und Taktsignale und zum Teil die Datensignale aufgrund von speziellen Hardwarekomponenten innerhalb des FPGAs an feste Pins oder zumindest Pingruppen geknüpft. Damit wäre vermutlich ein mindest sechslagiges Design nötig geworden.

Todo

Todo

Todo

Der DDR3 Speicher ist immer dynamischer Ram. Im Gegensatz zu statischem Ram, welcher die Information solange behält, wie die Betriebsspannung anliegt, "vergisst" dynamischer Speicher die Information durch Leckströme schon nach kurzer Zeit. Um dies zu verhindern wird mehrfach pro Sekunde ein Teil des Speichers ausgelesen und wieder direkt wieder neu gespeichert (Refresh Zyklus). Mit einem eigenen Controller kann man diesen Refresh natürlich auch testhalber ausschalten um zu sehen wie ein Verlust von Informationen in der Praxis aussieht.

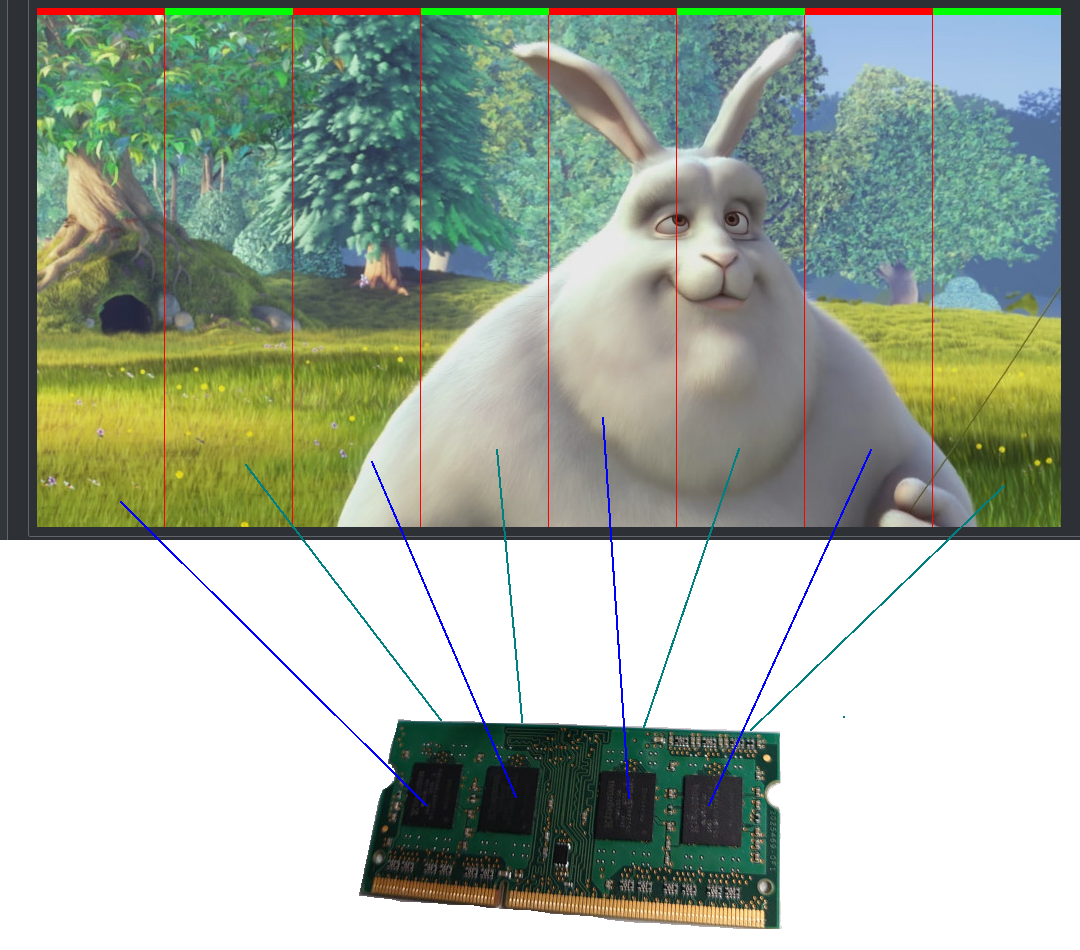

Im folgenden wurde ein Bild (Quelle: Film Big Buck Bunny, www.bigbuckbunny.org (C) Blender Foundation) als Bitmap eingespeichert und anschließend wieder ausgelesen. Dabei wurde das Bild in 8 Spalten geteilt und jede Speile auf einem separaten DDR3 IC gespeichert (das SODIMM Modul besteht aus jeweils aus vier ICs auf der Vorder- und Rückseite). Mit eingeschaltetem Refresh bleibt das Bild wie gewünscht beliebig lange erhalten.

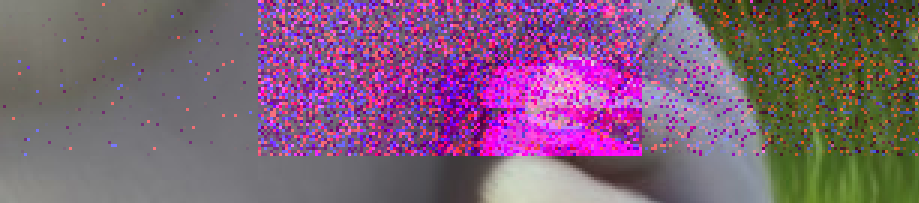

Schaltet man die Refresh Zyklen aus, so beginnt ein Zerfall der Information einzusetzen. Bei angelegter Betriebsspannung ist aber selbst nach ein paar Minuten ohne Refresh Zyklen ein großer Teil der Information erhalten geblieben:

Für sicherheitskritische Anwendungen sollte deshalb der Speicherbereich nach Beendigung auf jedenfall überschrieben werden.

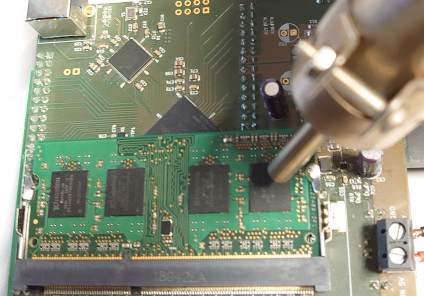

Der Zerfall ist auch temperaturabhängig. Bei dem folgenden Bild wurde mit einem Heißluftfön ein einzelner Speicher IC gezielt erwärmt. Schon nach wenigen Sekunden ist ein Großteil des dort gespeicherten Bildinhaltes zerstört (Spalte 7). Auch der IC auf der Rückseite des Moduls wurde durch die Platine hindurch etwas erwärmt, weshalb auch hier ein leichter Informationsverlust festgestellt werden kann (Spalte 8).

Schaltet man das RAM Modul komplett aus (ich habe es sogar aus dem Slot entfernt), so geht der Zerfall deutlich schneller vonstatten. Nach ein paar Sekunden ist ein Großteil der Information verschwunden. Aber komplett leer ist der Ram nicht. Außerdem scheint der Verlust der Information nicht auf jedem IC gleich schnell vonstatten gegangen zu sein.

Tiefgekühlte Daten bleiben auch ausgeschaltet länger "frisch":

Wer genau aufgepasst hat, wird bemerkt haben, dass die untersten Zeilen des Bildes nicht immer zerstört werden. Woran liegt das?

Um das zu verstehen, muss man ein Detail sowohl des DDR3 Speichers als auch des Controllers kennen: Der eigentliche Speicher wird nämlich nie direkt gelesen oder geschrieben. Stattdessen wählt man zunächst eine Speicherseite aus, die in einen im IC integrierten kleinen statischen Ram kopiert wird. Danach kann man diesen kleinen Bereich beliebig verändern. Sobald man eine andere Speicherseite auswählt, werden intern zunächst die vorherigen Änderungen der letzten Seite geschrieben. Da die unteren Bildzeilen als letztes geschrieben bzw. ausgelesen werden und der Speichercontroller eine Seite erst schließt, sofern eine andere aufgerufen wird, bleiben die letzten Bildzeilen die ganze Zeit im statischen Ram. Beim nächsten Auslesen werden sie dann frisch in den DRAM kopiert und kurze Zeit später erneut ausgelesen. Sie sind daher viel "jünger" im DRAM und deshalb fast gar nicht vom Zerfall betroffen. Das gilt natürlich nur solange, das Modul noch an die Betriebsspannung angeschlossen ist, denn andernfalls verliert auch der kleine integrierte SRAM seine Informationen recht zügig.

Noch größere Speichermengen sind mit DDR4 Speicher verfügbar. Mit einer Spannung von 1,2 Volt ist die Anbindung an einen MACHXO3 FPGA leider etwas schwierig. Der folgende Aufbau zeigt die Anbindung von DDR4 Speicher (auch SODIMM) an einen etwas größeren und mächtigeren FPGA, den Lattice ECP5:

Aufgrund der durch die COVID19 Situtation sind ICs schon seit zwei Jahren für kleine Unternehmen und Privatpersonen kaum mehr zuverlässig zu erhalten. Das Projekt ist deshalb derzeit pausiert.

Impressum | Datenschutzerklärung | [*]: externer Link | thilo.ackermann@gmail.com